为什么选择FPGA来做无人机飞控?

相比于目前主流的基于MCU(微控制器,如STM32)的飞控方案,FPGA具有以下核心优势:

| 特性 | FPGA方案 | MCU方案 | 对无人机的优势 |

|---|---|---|---|

| 并行处理能力 | 天生并行,可以同时执行多个独立的任务,每个任务由独立的硬件逻辑电路实现。 | 顺序执行,通过操作系统或轮询机制处理任务,本质上是串行的。 | 高实时性,传感器数据读取、控制算法解算、电机PWM输出等可以同时进行,延迟极低且稳定,这对于高速穿越、竞速等要求苛刻的场景至关重要。 |

| 确定性延迟 | 硬件决定延迟,一旦逻辑配置完成,任务的执行时间是固定的、可预测的,纳秒级。 | 软件决定延迟,受中断优先级、任务调度、代码复杂度影响,延迟是变化的,微秒到毫秒级。 | 控制更稳定,没有“意外”的延迟,控制律的执行周期极其精确,避免了因延迟抖动导致的控制性能下降甚至振荡。 |

| I/O处理能力 | 海量并行I/O,可以轻松处理数十路甚至上百路高速、高分辨率的PWM信号,或同时与多个传感器通信。 | I/O有限,受限于GPIO数量和通信总线(如SPI, I2C)的速度和数量。 | 驱动更多电机/设备,轻松实现八轴、十二轴甚至更多电机的控制,或同时连接多个高清图传、数据链等。 |

| 自定义算法 | 硬件级算法实现,可以将复杂的算法(如FIR滤波器、卡尔曼滤波、矩阵运算)直接用硬件逻辑实现,速度远超软件。 | 软件级算法实现,算法运行在CPU上,受限于时钟频率和指令集。 | 实现高级功能,在FPGA内部实现一个硬件级的传感器数据融合模块,处理速度和效率远超MCU上的软件实现。 |

| 硬件安全 | 逻辑隔离,不同功能模块(如传感器、电机、通信)的逻辑在物理上是隔离的,一个模块的故障不会轻易影响其他模块。 | 软件隔离,依赖操作系统或内存保护机制,隔离性较弱,一个软件错误可能导致整个系统崩溃。 | 系统更鲁棒,提高了系统的容错能力和安全性,尤其是在关键任务中。 |

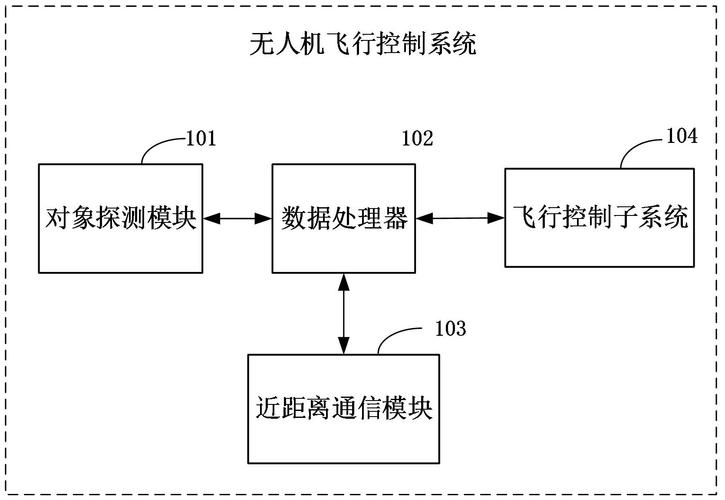

FPGA飞控系统的典型架构

一个基于FPGA的无人机飞控系统通常由以下几个部分构成,这些部分在FPGA内部以并行的方式运行。

-

传感器数据采集模块

- 功能:通过SPI或I2C接口,并行读取陀螺仪、加速度计、磁力计、气压计等传感器的数据。

- 实现:为每个传感器设计一个独立的SPI/I2C从机模块,它们可以同时向各自的总线发起读写请求,互不干扰。

-

数据融合与姿态解算模块

- 功能:融合传感器数据,解算出无人机的实时姿态(俯仰角、横滚角、偏航角)。

- 实现:这是FPGA的强项,可以用硬件逻辑实现一个卡尔曼滤波器或互补滤波器,相比于MCU上的软件滤波,硬件滤波器的延迟是固定的,吞吐量极高,可以处理更高频率的传感器数据,得到更平滑、更精确的姿态信息。

-

控制律解算模块

(图片来源网络,侵删)

(图片来源网络,侵删)- 功能:根据期望姿态(来自遥控器或自主导航算法)和当前姿态,计算出每个电机的控制量(通常是PID控制器)。

- 实现:为每个电机通道实现一个独立的PID控制器,这些控制器可以并行运行,同时计算出输出值,PID的P、I、D参数也可以通过软件接口动态配置。

-

PWM/ESC驱动模块

- 功能:将控制律解算出的数字量,转换成驱动电子调速器的PWM信号。

- 实现:一个高性能的PWM发生器,可以产生多路(如8路、12路)高分辨率(如16位)、高频率(如8kHz)的PWM信号,并支持相位微调等高级功能。

-

通信接口模块

- 功能:与遥控器(接收机)、上位机(地面站)、GPS模块、数传模块等进行数据交换。

- 实现:为每种通信协议(如SBUS, CRSF, UART, SPI, I2C)设计一个独立的硬件模块,并行处理收发数据,不占用主控制逻辑的时间。

-

系统管理与监控模块

- 功能:系统初始化、看门狗、状态监控、与外部处理器(如ARM核)交互等。

- 实现:通常FPGA内部会集成一个硬核ARM处理器(如Xilinx Zynq系列)或软核处理器(如MicroBlaze),这个处理器运行一个轻量级操作系统(如FreeRTOS),负责处理非实时性任务,如运行高层规划算法、与用户交互等,而FPGA部分则专注于底层的、实时的硬件控制任务,这种“FPGA + ARM”的异构架构是目前最主流的设计。

FPGA飞控 vs. MCU飞控:一个直观的对比

| 方面 | FPGA飞控 (如Xilinx Zynq) | MCU飞控 (如STM32F4) |

|---|---|---|

| 核心优势 | 极致的实时性、并行性、确定性 | 高性价比、生态成熟、开发简单 |

| 性能 | 纳秒级控制周期,延迟抖动趋近于零 | 微秒级控制周期,存在软件延迟抖动 |

| 开发难度 | 非常高,需要掌握Verilog/VHDL硬件描述语言、数字逻辑设计、时序分析。 | 相对较低,使用C/C++语言,基于成熟的库和框架(如PX4, ArduPilot)。 |

| 成本 | 高,FPGA芯片本身和开发工具都非常昂贵。 | 低,高性能MCU成本已降至非常低的水平。 |

| 灵活性 | 硬件级灵活,可以完全重新设计底层硬件架构,从零开始定制。 | 软件级灵活,在现有硬件平台上通过软件实现功能。 |

| 应用场景 | 高速竞速无人机、无人机集群控制、特种任务无人机、科研平台 | 消费级无人机、绝大多数商业级无人机、教学和DIY项目 |

主流FPGA平台与开发流程

主流平台

-

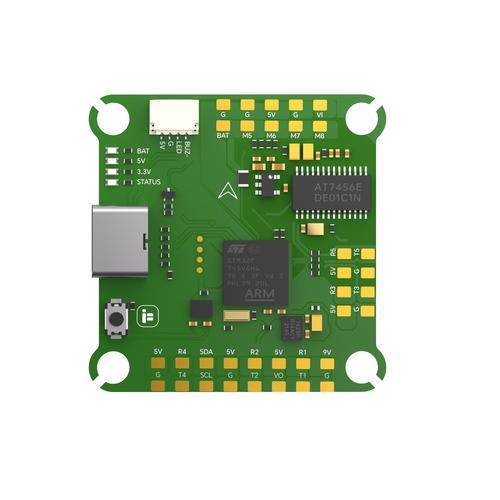

Xilinx Zynq / Zynq UltraScale+ MPSoC:这是业界最主流的选择,它将一个高性能ARM Cortex-A系列处理器(处理系统, PS)和FPGA逻辑(可编程逻辑, PL)封装在同一个芯片上。

(图片来源网络,侵删)

(图片来源网络,侵删)- PS (ARM核):运行Linux或FreeRTOS,负责高层应用、通信、算法复杂计算。

- PL (FPGA逻辑):负责底层实时任务,如传感器数据采集、PID控制、PWM生成。

- 这种架构完美结合了ARM的处理能力和FPGA的实时性,是目前FPGA飞控的“黄金标准”。

-

Intel (Altera) Cyclone / Arria / Stratix系列 + ARM硬核:与Xilinx方案类似,提供FPGA+ARM的SoC解决方案。

-

纯FPGA方案 + 外部MCU:在一些更定制的场景下,开发者可能使用一个纯FPGA芯片(不带ARM核),然后通过一个外部ARM MCU(如STM32H7)作为协处理器,负责非实时任务,两者通过高速总线(如AXI)通信。

开发流程

- 需求分析与架构设计:明确无人机需要哪些传感器、电机数量、通信协议等,并规划FPGA内部各个模块的划分和连接。

- 环境搭建:安装FPGA厂商的开发套件(如Xilinx Vitis/Vivado)。

- 模块化设计(HLS):

- 传统方式:使用Verilog或VHDL语言,从门电路层面设计每个功能模块。

- 现代方式:使用高层次综合工具,用C/C++或SystemC语言描述算法(如PID控制器),HLS工具会自动将其转换为RTL(寄存器传输级)代码,这大大加速了开发过程。

- 仿真与验证:在电脑上使用ModelSim等工具对设计的逻辑进行功能仿真,确保其行为正确。

- 实现与综合:将所有模块集成,进行逻辑综合、布局布线,生成比特流文件。

- 硬件调试:使用逻辑分析仪(如ChipScope, ILA)抓取FPGA内部的实际信号,验证硬件是否按预期工作。

- 系统联调:将生成的比特流文件烧录到FPGA中,与传感器、电机、飞控板等硬件连接,进行整机测试和参数整定。

挑战与未来趋势

挑战

- 开发门槛高:需要硬件设计背景,学习曲线陡峭。

- 成本高昂:芯片和开发工具的价格远超MCU。

- 功耗与散热:高性能FPGA功耗较大,在小型无人机上需要仔细考虑电源和散热设计。

- 生态不完善:不像STM32有丰富的开源库和社区支持,FPGA飞控需要开发者从零构建很多东西。

未来趋势

- AI/ML的硬件加速:将人工智能算法(如目标识别、路径规划的神经网络)在FPGA上硬件化,实现低功耗、高吞吐量的实时智能决策,让无人机更“聪明”。

- 无人机集群控制:FPGA的并行性和确定性使其成为控制大规模无人机集群的理想平台,可以处理集群内复杂的通信和协同逻辑。

- 更高级的传感器融合:集成更复杂的视觉传感器(如事件相机)和激光雷达,FPGA可以实时处理这些海量数据,实现更精确的环境感知。

- 设计工具的普及:随着HLS工具的成熟和更高层次抽象的出现,FPGA的开发门槛正在逐步降低,未来可能会有更多基于FPGA的飞控解决方案出现。

使用FPGA作为无人机飞控核心,是一种追求极限性能和最高可靠性的技术选择,它通过硬件并行和确定性执行,解决了MCU在高速、高精度控制场景下的瓶颈。

虽然目前它因其高成本和开发难度,主要应用于竞速、科研和特种领域,但随着AI、集群控制等前沿技术的发展,FPGA在无人机领域的应用前景将越来越广阔,对于希望深入无人机底层控制、从事前沿研究的工程师和爱好者来说,掌握FPGA飞控技术是一项非常有价值的技能。