制作手机CPU的技术是一个涉及多学科、多环节的复杂系统工程,需要从设计、制造、封装测试到软件优化全流程协同,其核心目标是在极小的芯片面积上集成数十亿个晶体管,实现高性能、低功耗与高能效的平衡,以下从关键技术环节、核心挑战及发展趋势等方面展开详细分析。

架构设计:性能与能效的基石

手机CPU的架构设计是决定其性能天花板的第一步,当前主流采用ARM架构(如Cortex系列),其精简指令集(RISC)设计相比复杂指令集(CISC)具有更高的执行效率和更低的功耗,具体而言:

- 核心架构:现代手机CPU普遍采用大小核设计(如“1+3+4”的1超大核+3大核+4小核),通过异构计算(Big.LITTLE架构)实现性能与功耗的动态调配,日常任务由小核处理,确保续航;高负载场景(如游戏、视频剪辑)由大核甚至超大核接管,满足性能需求。

- 微架构优化:通过流水线深度、分支预测、乱序执行等技术提升指令执行效率,以苹果A17 Pro的3nm工艺为例,其采用6个性能核和2个能效核,通过改进的ALU(算术逻辑单元)设计,单核性能较前代提升10%,同时能效比提升20%。

- AI引擎集成:随着AI应用的普及,CPU中普遍集成NPU(神经网络处理单元)或AI加速模块,如高通的Hexagon处理器、华为的NPU单元,通过专用硬件加速AI运算,减轻CPU负担。

制程工艺:纳米级精度的极限挑战

制程工艺是决定芯片集成度、功耗和成本的核心环节,目前最先进的已达到3nm、2nm级别,其关键技术包括:

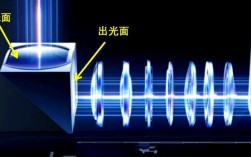

- 光刻技术:光刻是芯片制造的核心步骤,需将电路图案从掩模版转移到晶圆上,EUV(极紫外光刻)技术已成为7nm以下工艺的标配,相比传统DUV(深紫外光刻),EUV以13.5nm波长实现更高精度,可支持更复杂的电路设计,台积电3nm工艺采用EUV多次曝光,最小线宽可达12-14nm,晶体管密度较7nm提升约70%。

- 晶体管结构:随着制程进入纳米级别,传统平面晶体管(Planar FET)因量子隧效应导致漏电问题,FinFET(鳍式场效应晶体管)成为主流,3nm工艺进一步引入GAA(环绕栅极)结构,如三星3nm工艺采用MBCFET(多桥通道场效应晶体管),栅极完全包裹沟道,有效控制漏电,提升电流驱动能力。

- 材料与工艺创新:为突破硅材料的物理极限,引入高k金属栅极(HKMG)、应变硅、稀土元素等材料,Intel 20nm工艺首次采用HKMG,通过提高栅介质介电常数,降低漏电流;而3nm工艺可能引入二维材料(如二硫化钼)作为沟道材料,进一步提升性能。

芯片设计与EDA工具:亿级晶体管的协同管理

手机CPU的晶体管数量已达数百亿级别(如苹果A17 Pro包含近200亿个晶体管),需借助EDA(电子设计自动化)工具完成设计、验证与优化:

- IP核复用:CPU设计采用IP核(知识产权核)模块化设计,如ARM Cortex-A系列核、Imagination GPU核等,企业通过购买IP核快速集成功能模块,缩短开发周期。

- 布局布线优化:在纳米级工艺下,晶体管间距极小,需通过AI辅助的EDA工具进行布局布线,避免信号干扰、串扰等问题,Synopsys的DC(Design Compiler)工具可自动优化逻辑门布局,提升时序收敛效率。

- 3D IC设计:为突破2D平面集成度的限制,引入3D IC技术,如台积电的SoIC(系统级集成)工艺,将多层芯片堆叠互联,实现更高集成度和更短互连延迟,提升性能。

封装与测试:从裸片到成品的关键一步

芯片制造完成后,需通过封装和测试实现功能完整性和可靠性:

- 先进封装技术:传统封装(如QFP)已无法满足手机芯片的高集成度需求,转而采用Flip Chip(倒装焊)、SiP(系统级封装)等技术,苹果A15 Bionic采用InFO_oS(集成扇型基板封装),将CPU、GPU、NPU等芯片封装在同一基板上,减少面积和功耗;而华为麒麟9000S则采用芯粒(Chiplet)技术,将不同功能的小芯片封装在一起,提升良率。

- 测试与验证:芯片测试包括晶圆测试(CP)和成品测试(FT),需检测晶体管特性、电路功能、功耗等指标,自动测试设备(ATE)如泰瑞达的UltraFLEX,可同时测试多颗芯片,确保良率;通过扫描电镜(SEM)、X射线检测等手段封装缺陷。

软件与生态:硬件潜力的释放

硬件性能的发挥离不开软件优化:

- 操作系统适配:Android和iOS系统针对CPU架构进行深度优化,如Android的ART虚拟机支持AOT(提前编译),提升应用执行效率;iOS的Metal框架直接调用GPU硬件加速,减少CPU开销。

- 编译器优化:编译器(如GCC、Clang)通过指令调度、循环展开等技术,将代码转化为CPU最高效执行的指令序列,针对ARM NEON指令集的优化,可显著提升多媒体处理性能。

核心挑战与发展趋势

- 挑战:制程工艺逼近物理极限(如量子隧效应、散热问题);先进制程成本高昂(3nm研发成本超200亿美元);异构计算复杂性增加,软件开发难度加大。

- 趋势:

- Chiplet技术普及:通过小芯片堆叠降低成本,提升良率。

- 3D集成深化:如台积电的SoIC、Intel的Foveros,实现多层芯片垂直互联。

- AI驱动设计:AI用于EDA工具优化、芯片设计自动化,如谷歌利用AI设计TPU芯片。

- 新材料探索:碳纳米管、石墨烯等新材料有望替代硅,突破性能瓶颈。

相关问答FAQs

Q1:为什么手机CPU要采用大小核设计,而不是单纯的高性能核?

A1:大小核设计(异构计算)的核心目标是平衡性能与功耗,高性能核(如Cortex-X系列)处理高负载任务时性能强劲,但功耗较高;小核(如Cortex-A510)专注于日常任务(如社交、导航),功耗仅为高性能核的1/5甚至更低,通过操作系统(如Android的LRU算法、iOS的电源管理)动态调度任务,既保证了流畅体验,又延长了续航时间,若单纯使用高性能核,即使待机功耗也会显著增加,无法满足手机对续航的需求。

Q2:制程工艺从7nm升级到3nm,手机CPU的实际体验提升有多大?

A2:制程升级带来的体验提升是多维度的,以台积电7nm和3nm工艺对比为例:

- 性能:3nm晶体管密度提升70%,相同性能下功耗降低30%-50%,或相同功耗下性能提升15%-20%,A17 Pro的3nm芯片较A16的4nm芯片,单核性能提升10%,能效比提升20%,游戏帧率更稳定,发热更低。

- 续航:3nm芯片的能效提升直接转化为续航增长,若保持电池容量不变,手机续航可延长10%-15%。

- 功能集成:更小的制程允许在相同面积内集成更多晶体管,如NPU算力从7nm的15 TOPS提升至3nm的35 TOPS,支持更复杂的AI应用(如实时AI视频增强)。

但实际体验还受架构设计、软件优化等因素影响,例如若应用未针对新架构优化,性能提升可能不明显。