Foveros封装技术是英特尔推出的一种先进的三维(3D)芯片封装技术,它代表了半导体封装领域从传统平面布局向立体堆叠的重大转变,这项技术的核心在于通过将多个不同功能的芯片(如计算核心、I/O芯片、内存等)垂直堆叠在一起,实现更高密度、更高性能和更低功耗的集成,从而突破传统二维封装在互连密度、带宽和功耗方面的物理限制,Foveros的名称来源于拉丁语“fovere”,意为“加热”或“赋予生命”,寓意着该技术为芯片设计注入了新的活力,推动了计算能力的持续进化。

技术原理与架构特点

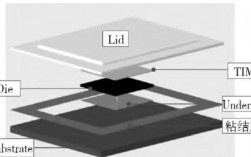

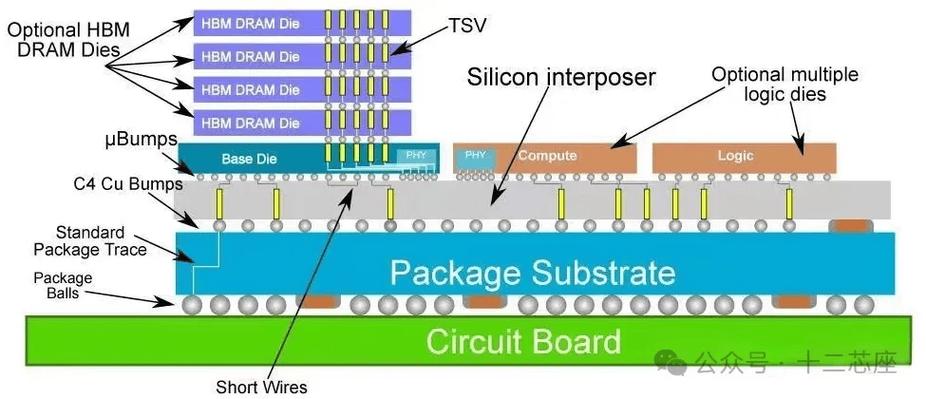

Foveros封装技术的核心在于其“3D堆叠+混合集成”的设计理念,与传统封装技术(如传统的基板封装或2.5D封装)将芯片并排放置在封装基板上不同,Foveros直接将裸芯片(Die)垂直堆叠,形成类似摩天大楼的三维结构,这种堆叠并非简单的叠加,而是通过微小的硅通孔(TSV,Through-Silicon Via)和微凸块(Microbump)实现芯片之间的电气连接,TSV是在芯片硅片上钻出的深孔,用于垂直信号传输;微凸块则是芯片与芯片之间的“桥梁”,负责实现高密度的互连。

Foveros的架构通常分为三个层次:底层(Base Die)、中间层(Logic Die)和顶层(I/O Die或Memory Die),底层芯片通常采用先进的制程工艺(如10nm或7nm),集成了高性能的计算核心,负责主要的运算任务;中间层可以根据需求堆叠多个功能芯片,如AI加速单元、图形处理单元等;顶层芯片则主要负责I/O接口(如PCIe、USB、内存接口)和电源管理,直接与外部组件连接,这种分层设计允许不同制程、不同功能的芯片灵活组合,例如将先进的计算核心与成熟的I/O芯片集成,既保证了性能,又控制了成本。

关键技术突破

Foveros封装技术的实现依赖于多项关键技术的突破,首先是高密度互连技术,通过微凸块实现芯片之间高达数百万个连接点,互连密度相比传统封装提升了10倍以上,大幅降低了信号传输延迟和功耗,其次是异构集成能力,Foveros支持将不同制程(如10nm逻辑芯片与22nm I/O芯片)、不同材料(如硅、化合物半导体)的芯片集成在一起,实现了“量体裁衣”式的芯片设计,避免了将所有功能都集成在单一芯片上的复杂性和高成本。

Foveros还采用了先进的散热设计,由于三维堆叠会导致热量集中,英特尔在封装中集成了微型散热通道和高效的热界面材料(TIM),通过底部散热模块(如散热器或热管)快速导出热量,确保芯片在高温环境下仍能稳定运行,Foveros的模块化设计也提高了生产灵活性,底层芯片可以作为“平台”支持多种上层芯片的组合,缩短了产品开发周期,降低了研发成本。

应用场景与优势

Foveros封装技术的应用场景广泛,尤其在高性能计算、人工智能、移动设备和数据中心等领域展现出巨大潜力,在移动设备中,Foveros可以将高性能处理器与低功耗I/O芯片堆叠,在缩小设备尺寸的同时提升性能和续航;在AI领域,通过将计算核心与专用AI加速芯片集成,可以实现更高的算力和能效比;在数据中心,Foveros支持将CPU、GPU和内存控制器等组件高度集成,提高服务器密度和计算效率。

相比传统封装技术,Foveros的优势主要体现在三个方面:一是性能提升,垂直堆叠缩短了信号传输路径,降低了延迟,提高了数据带宽;二是功耗优化,高密度互连减少了长距离布线的能量损耗,同时支持更精细的电源管理;三是设计灵活性,异构集成允许开发者根据需求选择最适合的芯片组合,避免“一刀切”的设计模式,这些优势使得Foveros成为后摩尔时代提升芯片性能的重要技术路径。

技术挑战与未来发展方向

尽管Foveros封装技术带来了诸多突破,但其实现仍面临挑战,首先是良率问题,三维堆叠涉及多个芯片的精确对位和 bonding,工艺复杂度高,任何一层的缺陷都可能导致整个封装失效,这对制造工艺提出了极高要求,其次是成本问题,高密度互连和TSV工艺增加了生产成本,目前主要应用于高端芯片领域,未来需要通过技术优化降低成本以实现更广泛的应用,散热问题仍然是三维堆叠的关键挑战,随着堆叠层数增加,热量管理难度进一步加大,需要开发更高效的散热材料和结构。

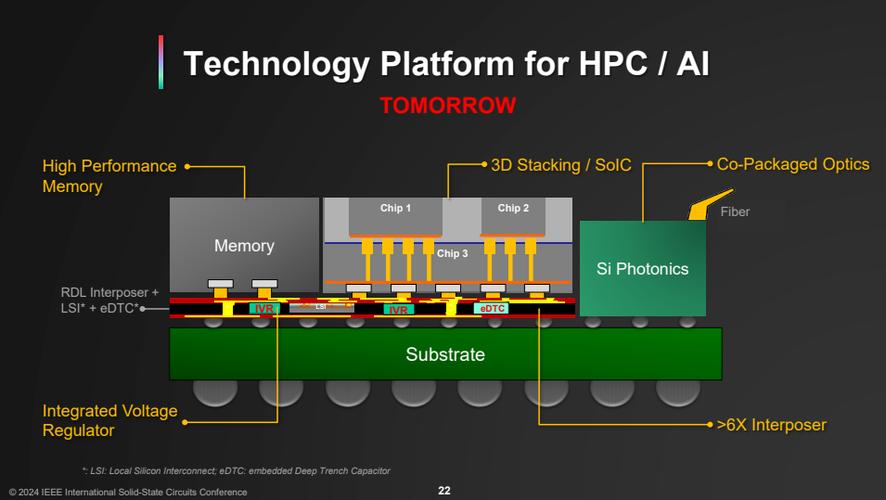

Foveros技术有望向更高层数堆叠、更小互连尺寸和更广泛的异构集成方向发展,结合英特尔的EMIB(Embedded Multi-Die Interconnect Bridge)技术,Foveros可以实现更大规模的芯片集成;与光互连技术结合,可以进一步提升带宽并降低功耗,随着AI和物联网设备的普及,Foveros在边缘计算和低功耗芯片领域的应用也将不断拓展,成为推动半导体产业创新的重要引擎。

相关技术对比

为了更直观地理解Foveros的优势,以下将其与传统封装技术及2.5D封装进行对比:

| 技术类型 | 互连方式 | 集成密度 | 性能提升 | 功耗优化 | 应用场景 |

|---|---|---|---|---|---|

| 传统2D封装 | 基板布线 | 低 | 有限 | 有限 | 通用芯片、消费电子 |

| 5D封装(如EMIB) | 中介层+硅通孔 | 中 | 中等 | 中等 | 高性能计算、GPU |

| Foveros 3D封装 | 芯片间微凸块+硅通孔 | 高 | 显著 | 显著 | 高端移动设备、AI、数据中心 |

相关问答FAQs

问题1:Foveros封装技术与传统的2.5D封装(如EMIB)有何本质区别?

解答:两者的核心区别在于芯片堆叠方式和集成密度,2.5D封装(如EMIB)通过中介层(Interposer)将多个芯片并排放置在基板上,芯片之间通过中介层的布线连接,本质上仍是平面布局的延伸,而Foveros采用真正的3D堆叠,直接将芯片垂直堆叠,通过微凸块实现芯片间的直接互连,集成密度和互连效率更高,能够实现更紧凑的设计和更低的延迟。

问题2:Foveros封装技术的成本是否过高,会影响其普及吗?

解答:目前Foveros封装技术的成本确实较高,主要由于高密度互连、TSV工艺和复杂的生产流程,随着技术成熟和量产规模扩大,成本有望逐步降低,Foveros的高性能和能效优势能够为高端芯片(如AI处理器、旗舰级移动芯片)带来显著价值,因此在高端领域具有不可替代性,通过模块化设计和工艺优化,Foveros可能会向中端市场渗透,实现更广泛的应用。