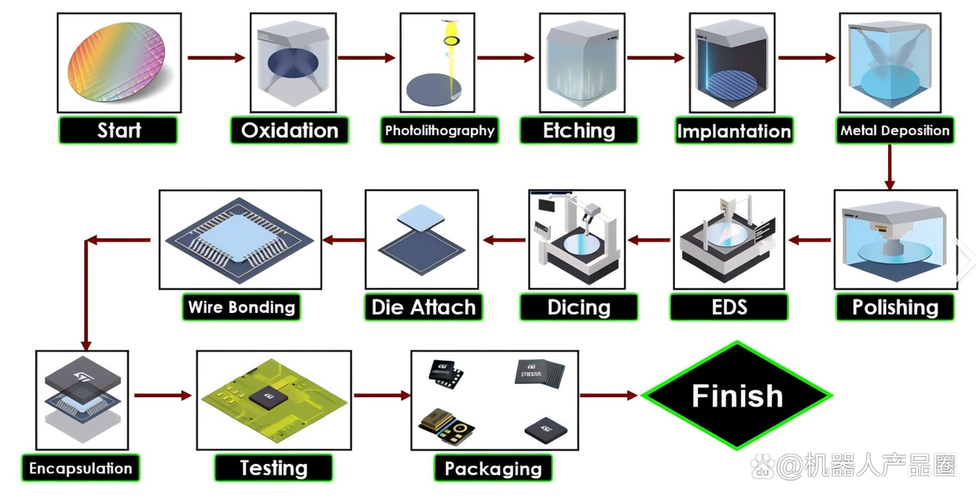

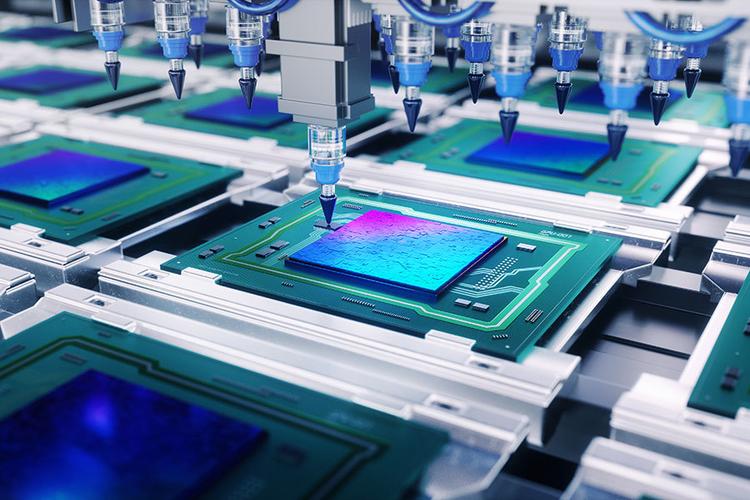

集成电路芯片制造工艺技术是现代信息社会的核心基石,涵盖了从硅片制备到最终芯片封装测试的全流程,其技术水平直接决定了芯片的性能、功耗和成本,整个制造过程如同在微观尺度上进行的“建筑工程”,需要结合光刻、刻蚀、薄膜生长、离子注入等上百道精密工序,最终在硅片上构建出数以亿计的晶体管和互连结构。

制造工艺的核心始于硅片的制备,高纯度单晶硅通过直拉法或区熔法制成硅锭,再经切割、研磨和抛光形成直径300mm或更小的晶圆,表面平整度需达到原子级精度,随后进入前道工序,其中光刻是关键步骤,通过涂胶、曝光、显影将电路图形转移到晶圆表面,目前最先进的光刻机采用极紫外光(EUV)技术,可实现7nm及以下节点的图形化,刻蚀工艺则利用等离子体或化学反应去除未被保护的材料,形成精确的沟槽和结构,干法刻蚀中的反应离子刻蚀(RIE)和深反应离子刻蚀(DRIE)应用广泛,薄膜生长通过化学气相沉积(CVD)或物理气相沉积(PVD)在晶圆表面形成绝缘层、导电层或阻挡层,其中原子层沉积(ALD)可实现原子级精度的薄膜控制,离子注入则是通过高能离子束掺杂硅片,改变导电类型,形成PN结和晶体管源漏区。

随着制程节点不断缩小,晶体管结构也从传统的平面型演变为FinFET(鳍式场效应晶体管)和GAAFET(环绕栅极晶体管),以增强沟道控制能力,抑制漏电流,5nm节点采用GAAFET结构,栅极完全包裹纳米线沟道,显著提高了开关比和能效,互连技术同样面临挑战,铜互连和低介电常数介质(Low-k)材料的应用降低了RC延迟,而3D集成技术如硅通孔(TSV)和芯片堆叠,实现了垂直方向上的芯片互连,大幅提高了集成度。

制造过程中的质量控制至关重要,每道工序后都需要通过检测设备(如扫描电子显微镜SEM、原子力显微镜AFM)进行形貌和尺寸检测,电学测试则验证器件性能,良率管理是降低成本的关键,需通过统计过程控制(SPC)和缺陷分析确保工艺稳定性。

以下为部分关键工艺参数对比:

| 工艺环节 | 28nm节点 | 7nm节点(EUV) | 3nm节点(GAA) |

|---|---|---|---|

| 光刻光源 | 193nm深紫外 | 5nm极紫外 | 极紫外多重曝光 |

| 晶体管结构 | 平面晶体管 | FinFET | GAAFET |

| 互连金属 | 铜/低-k介质 | 铜/超低-k介质 | 钴/钌等新型金属 |

| 关键尺寸 | 28nm | 7-10nm | 3-5nm |

相关问答FAQs:

-

问:为什么芯片制造工艺节点越小,芯片性能越好?

答:工艺节点缩小意味着晶体管尺寸更小,可在相同面积内集成更多晶体管,提升计算密度,缩短了晶体管沟道长度,降低了开关延迟和功耗,使芯片运行速度更快、能效更高,但小尺寸也会带来量子隧穿效应等挑战,需通过新型结构(如FinFET、GAA)克服物理极限。 -

问:EUV光刻技术为何对先进制程至关重要?

答:传统193nm光刻机通过多重曝光实现小尺寸图形,但成本高、效率低且缺陷风险大,EUV光刻使用13.5nm极紫外光,可直接刻印更精细的图形,减少曝光次数,提升良率和生产效率,它是7nm及以下节点不可或缺的核心技术,解决了传统光刻在物理分辨率上的瓶颈。