2025年,半导体行业在CMOS技术领域取得了突破性进展,特别是在先进制程节点的量产和新型器件结构的引入方面,这一年,台积电、三星等代工厂率先实现了7nm工艺的规模化生产,同时5nm工艺也进入试产阶段,标志着摩尔定律在晶体管密度和性能提升上依然展现出强劲的生命力,FinFET(鳍式场效应晶体管)技术持续优化,而GAA(环绕栅极)架构作为FinFET的潜在替代方案开始在实验室和早期生产线中崭露头角,为3nm及以下节点的技术突破奠定了基础。

在7nm工艺的量产过程中,多重曝光技术的成熟应用成为关键,相较于上一代10nm工艺,7nm通过采用深紫外(DUV)多重曝光或极紫外(EUV)光刻技术,显著提升了晶体管密度和芯片性能,台积电的7nm N7工艺采用EUV光刻,减少了光罩层数,提高了生产效率,同时通过优化晶体管结构和金属互连方案,实现了性能提升20%、功耗降低40%或密度提升60%的多重目标,三星则在其7nm LPP(Low Power Plus)工艺中引入了EUV技术,并针对高性能计算(HPC)和移动应用场景推出了差异化版本,进一步扩大了7nm工艺的市场覆盖范围,7nm工艺在功耗控制方面也取得了显著进步,通过引入超低功耗(ULP)晶体管设计和动态电压频率调整(DVFS)技术,满足了移动设备对续航能力的严苛要求。

随着制程节点向5nm及以下推进,传统FinFET结构的局限性逐渐显现,当鳍片尺寸缩小至5nm以下时,栅极对沟道的控制能力减弱,短沟道效应(SCE)导致漏电流增加,影响芯片的稳定性和功耗,为此,GAA架构成为行业关注的焦点,与FinFET的“鳍片-栅极”单面接触不同,GAA结构采用纳米线(Nanowire)或纳米片(Nanosheet)作为沟道,栅极完全环绕沟道,从而实现对电流的更精准控制,2025年,三星率先宣布其3nm GAA工艺进入研发后期,计划在2025年试产;台积电也透露其2nm工艺将采用类似GAA的架构,GAA技术的引入不仅能够有效抑制短沟道效应,还能在相同功耗下提升晶体管性能,或在相同性能下降低功耗,为未来5-7年的技术迭代提供了明确路径。

在材料创新方面,2025年CMOS技术的一个重要突破是应变硅和高k金属栅(HKMG)技术的进一步优化,7nm及以下工艺中,硅锗(SiGe)和碳化硅(SiC)等应变材料被引入PMOS和NMOS晶体管中,通过改变硅晶格结构来载流子迁移率,从而提升驱动电流,HKMG技术中的金属栅电极材料从传统的铝铜合金转向钴(Co)或钌(Ru),以降低电阻并提高栅极稳定性,二维材料(如二硫化钼,MoS2)和碳纳米管等新型半导体材料在实验室中展现出潜力,虽然尚未进入量产阶段,但为后CMOS时代的器件设计提供了新思路。

互连技术的进步同样是2025年CMOS发展的重要方向,随着晶体管密度的提升,金属互连线的RC(电阻-电容)延迟成为制约芯片性能的关键因素,为此,7nm工艺中开始采用更低电阻的铜互连和更低介电常数(k值)的介电材料,如碳掺杂氧化硅(SiCOH),以降低信号延迟和功耗,台积电在7nm工艺中引入了“超级接触”(Super Contact)技术,通过优化接触孔结构,进一步降低了接触电阻,提升了芯片的可靠性。

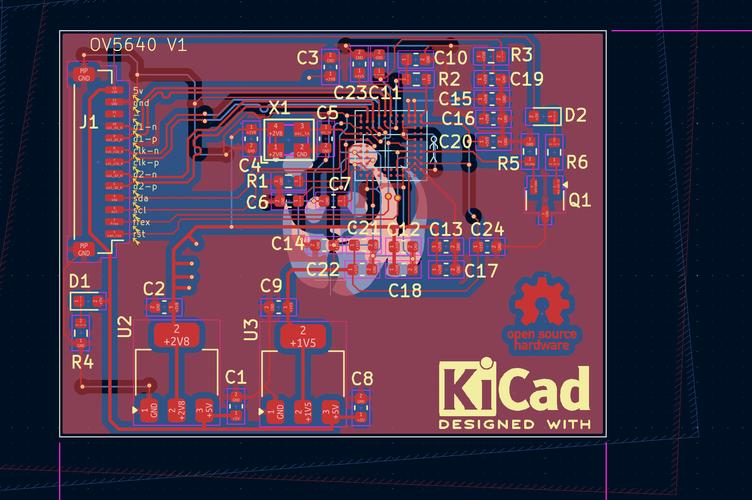

除了工艺和材料的创新,2025年CMOS技术在设计方法和EDA工具方面也取得了显著进展,为了应对先进制程带来的设计复杂度挑战,电子设计自动化(EDA)工具厂商推出了支持3D IC设计、光刻工艺仿真和功耗分析的全新解决方案,针对EUV光刻的邻近效应修正(OPC)算法得到优化,提高了光刻图形的精度;人工智能(AI)技术被引入EDA流程,通过机器学习加速布局布线和时序收敛,缩短了芯片设计周期。

2025年的CMOS技术发展也面临诸多挑战,先进制程的研发和生产线建设成本急剧上升,7nm工艺的晶圆成本达到1万美元以上,导致只有少数头部企业能够承担先进芯片的制造费用;量子效应和工艺偏差问题在5nm以下节点愈发突出,对芯片良率和可靠性构成威胁,全球半导体产业链的地缘政治因素也开始影响CMOS技术的全球化协作,例如美国对华为等企业的技术限制,使得部分企业在先进制程获取上面临困难。

以下是2025年CMOS技术关键进展的简要对比:

| 技术方向 | 7nm工艺进展 | 5nm及以下技术趋势 |

|---|---|---|

| 晶体管结构 | FinFET优化,鳍片宽度进一步缩小 | GAA架构(纳米线/纳米片) |

| 光刻技术 | EUV量产应用(台积电、三星) | 多重EUV+高NA EUV研发 |

| 材料创新 | SiGe/SiC应变材料,Co/Ru金属栅 | 二维材料探索,高k介质优化 |

| 互连技术 | 低k介电材料,超级接触技术 | 纳米级铜互连,3D集成 |

| 设计与EDA | AI辅助设计,3D IC仿真 | 量子效应建模,良率提升工具 |

相关问答FAQs:

Q1:2025年7nm工艺相比10nm工艺有哪些核心优势?

A1:2025年7nm工艺的核心优势体现在三个方面:一是晶体管密度提升60%,可在相同芯片面积内集成更多功能;二是性能提升20%,通过优化晶体管结构和EUV光刻技术实现更高的开关速度;三是功耗降低40%,得益于超低功耗晶体管设计和动态电压频率调整技术,特别适用于移动设备和数据中心应用,7nm工艺通过减少光罩层数(如台积电采用EUV减少约15%光罩),降低了生产成本和周期。

Q2:GAA架构为何被视为FinFET的替代方案?其技术难点是什么?

A2:GAA架构被视为FinFET的替代方案,主要因为其栅极完全环绕沟道(纳米线或纳米片),相比FinFET的单面栅极接触,能更有效地抑制短沟道效应,提升对电流的控制能力,这使得GAA在5nm及以下节点可实现更低的漏电流和更高的驱动电流,技术难点包括:纳米线/纳米片的精确制造工艺(如刻蚀和沉积均匀性控制)、栅极环绕结构的复杂集成、以及良率提升的挑战,GAA对工艺波动更敏感,需要更先进的EDA工具进行仿真和优化。