什么是 Power Gating?(核心思想)

Power Gating,中文常译为 电源门控 或 电源开关,其核心思想非常直观:

通过一个“开关”来完全切断或恢复向芯片上某个不工作的功能模块(如CPU核心、GPU、DSP等)的供电,从而消除其静态功耗(漏电流功耗)。

可以把芯片想象成一栋大楼,不同的功能模块(CPU、GPU、内存控制器等)就像大楼里不同的办公室或区域,当某个区域(比如一个CPU核心)下班后,我们不会只是关掉里面的灯(降低动态功耗),而是会直接切断整个区域的供电(拉下电闸),这样连墙上的插座、空调待机的功耗(静态功耗)都没有了。

为什么需要 Power Gating?(解决的问题)

要理解它的必要性,我们首先要了解芯片功耗的两个主要来源:

-

动态功耗:由电路在0和1状态翻转时产生,与芯片的工作频率和电压成正比,公式为

P_dynamic ∝ C * V² * f。 (图片来源网络,侵删)

(图片来源网络,侵删)- 解决方法:可以通过动态电压频率调节来降低,当芯片负载不高时,降低工作电压和频率,可以有效减少动态功耗。

-

静态功耗:也称为漏电流功耗,即使电路不工作(时钟停止),由于晶体管的物理特性,电流也会从电源流向地,形成微小的漏电流,随着工艺尺寸越来越小(从7nm到5nm、3nm),晶体管的漏电流问题越来越严重,静态功耗在总功耗中的占比也越来越高,有时甚至超过动态功耗。

- 解决方法:传统的DVFS无法消除静态功耗,这时,Power Gating 就派上用场了,它能从物理上隔绝电源,将静态功耗降至接近于零。

DVFS是“节能模式”,而Power Gating是“深度睡眠模式”。

Power Gating 是如何工作的?(基本原理)

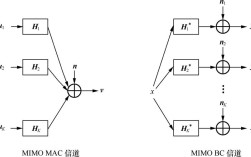

Power Gating 的实现依赖于两个关键组件:

a. 电源门控开关

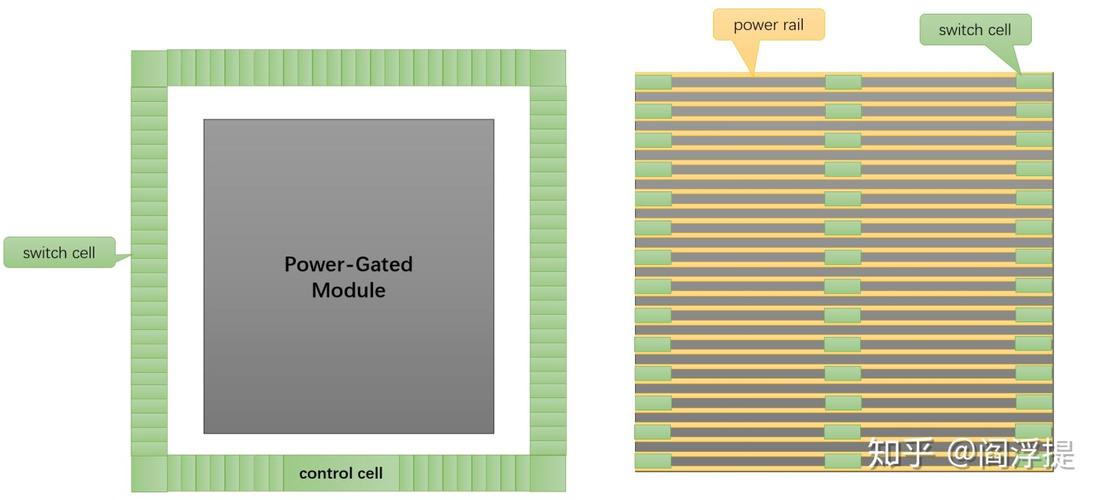

这是整个技术的核心,它不是一个普通的开关,而是一个特殊的、由多个晶体管构成的复杂电路,通常被称为 Fine-Grain Power Gating (FGPG) 或 Clustered Power Gating。

- 结构:它通常由一个低阈值电压的P型晶体管和一个高阈值电压的N型晶体管组成。

- P-FinFET (P-type):作为“主开关”,连接到电源域,它用低Vt晶体管是为了保证开关速度足够快,能快速为整个功能模块上电。

- N-FinFET (N-type):作为“保持开关”或“隔离开关”,连接到地,它用高Vt晶体管是为了在关闭状态下,自身的漏电流极小,从而避免引入新的功耗问题。

b. 控制逻辑

这部分负责向PG开关发送“开启”和“关闭”的指令。

- 控制信号:

clamp/isolate(隔离信号):在断电前,该信号有效,将模块的输出与下游模块隔离,防止断电后输出端的浮空状态对其他部分造成干扰。save:保存模块内部的关键寄存器状态(程序计数器PC、关键数据等)。power-gate control(门控信号):真正的“开关”信号。0表示关闭(切断电源),1表示开启(恢复供电)。

工作流程:

关闭流程(进入睡眠):

- 步骤1:CPU或操作系统决定让某个核心进入睡眠状态。

- 步骤2:控制逻辑发出

clamp和save信号,保存该核心的状态并隔离其输出。 - 步骤3:控制逻辑将

power-gate control信号置为0。 - 步骤4:PG开关的P-FinFET和N-FinFET都断开,该核心的VDD(电源)和VSS(地)被完全切断,静态功耗被消除。

开启流程(唤醒):

- 步骤1:接收到外部中断(如触摸屏点击、网络数据包到达)或内部定时器中断。

- 步骤2:控制逻辑将

power-gate control信号置为1。 - 步骤3:PG开关的P-FinFET(低Vt)迅速导通,为整个核心模块的电容充电,恢复电压,这个过程会产生一个较大的上电电流。

- 步骤4:电压稳定后,N-FinFET导通,为地线提供回路。

- 步骤5:核心内的复位信号释放,从之前保存的状态恢复,开始正常工作。

Power Gating 的类型

根据门控的精细程度,可以分为两类:

a. 细粒度电源门控

- 描述:对芯片内部非常小的单元(甚至单个标准单元)进行独立的电源控制。

- 优点:节能效果最好,可以实现最精细的功耗控制。

- 缺点:控制逻辑极其复杂,需要大量的PG开关,会占用大量芯片面积,并可能影响电路性能和时序。

- 应用:通常用于对面积和性能要求不那么苛刻,但对功耗极其敏感的特定逻辑块。

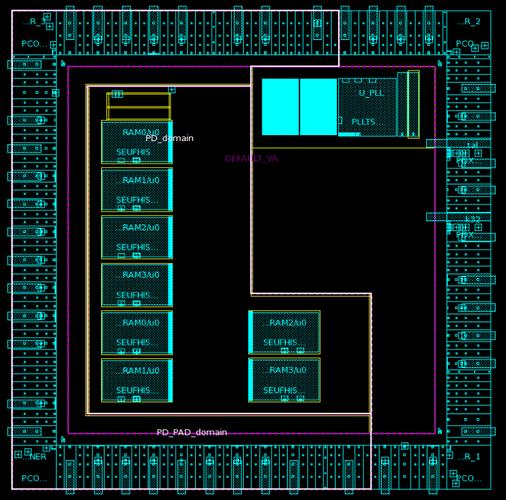

b. 粗粒度电源门控

这是目前最主流和最常用的方式。

- 描述:将芯片划分为几个大的功能域(如一个CPU簇、GPU、NPU、内存控制器等),对整个大的功能域进行统一的电源控制。

- 优点:控制逻辑相对简单,面积开销小,易于实现和管理。

- 缺点:节能效果不如细粒度,因为一个域内可能只有部分单元在工作,但整个域都被一起关闭或开启。

- 应用:现代移动SoC(如高通骁龙、苹果A系列、华为麒麟)中的CPU核心簇、GPU等,普遍采用粗粒度Power Gating。

优点与缺点

优点:

- 显著降低静态功耗:是其最大的优势,尤其是在先进工艺节点上。

- 延长电池续航:对于移动设备至关重要。

- 满足绿色环保要求:符合数据中心和消费电子产品的能效标准。

缺点与挑战:

- 唤醒延迟:从断电到恢复供电并开始工作需要一定时间(微秒级别),不适合需要快速响应的场景。

- 上电电流冲击:唤醒瞬间的大电流可能对芯片的电源管理单元造成压力,需要良好的电源完整性设计。

- 面积开销:PG开关本身和控制逻辑会占用宝贵的芯片面积。

- 设计复杂性:引入了新的时序和验证问题,设计流程更复杂。

实际应用场景

Power Gating 已经成为现代SoC的标配技术:

- CPU/GPU:当系统负载低时,可以关闭部分核心或整个GPU,只保留一个或几个小核心(如ARM的Cortex-A53)来处理后台任务。

- DSP/NPU:在不需要进行数字信号处理或AI计算时,将其完全关闭。

- 连接模块:如Wi-Fi、蓝牙、5G基带在不使用时被断电。

- 内存控制器:当内存处于空闲状态时,可以进入低功耗模式。

| 特性 | 描述 |

|---|---|

| 核心目标 | 消除功能模块的静态功耗(漏电流)。 |

| 实现方式 | 通过一个电源门控开关来控制电源的通断。 |

| 工作模式 | DVFS(动态电压频率调节)是“节能”,Power Gating是“深度睡眠”。 |

| 主要类型 | 粗粒度(主流,对大功能域操作)和细粒度(对微小单元操作)。 |

| 关键优势 | 在先进工艺下,对延长电池寿命至关重要。 |

| 主要挑战 | 唤醒延迟、上电电流冲击和设计复杂性。 |

Power Gating 是一项通过“牺牲”一部分唤醒速度和设计复杂度,来换取极致静态功耗降低的关键技术,是现代低功耗芯片设计不可或缺的一环。